2024

Aug.27, 2024

MINEBEA MITSUMI Inc.

ABLIC launches S-34HTS08AB, DDR5 SPD IC for Client/Server DIMM

- I3C high-speed communication standard compliant, and equipped with a HUB function to contribute to processing of large volumes of data -

MinebeaMitsumi Group

Green Products

ABLIC (President: Seiji Tanaka, Head Office: Minato-ku, Tokyo; hereinafter "ABLIC"), a group company of MinebeaMitsumi Inc., today launched the S-34HTS08AB SPD IC for DDR5 memory modules.

The amount of communication data handled by client PCs and data center servers has been growing at a rapid rate, resulting in demand for higher level data processing capacity in memory modules. In addition, the standard for memory modules is also shifting from the previous DDR4 to DDR5 which has faster processing speeds and is capable of processing greater amounts of data.

In order to achieve this new structure, DDR5 SPD adds a HUB function to mediate communication among devices as well as support for the I3C standard for high-speed communication, which is an extension of the I2C standard, in addition to the EEPROM function and temperature sensor functions also found on existing DDR4. The new S-34HTS08AB product launched today is compliant with SPD5118 which is the latest JEDEC (*1) specification for DDR5 SPD, and is also equipped with a HUB function. In addition, it is also compatible with both the I2C and I3C communication standards, which increases operation speed from 1MHz up to 12.5MHz and allows for proper control of communications between external controllers and devices on the DIMM board. These features enable advanced data processing capabilities and allow for a wide range of use as DDR5 DIMM ICs for clients and servers. Furthermore, the input output circuits are designed using ABLIC's proprietary technologies and knowhow to achieve high-speed and stable communication and a high degree of compatibility with peripheral devices from other manufacturers, making this product perfect for customers who want to make flexible purchases.

On the launch of the new S-34HTS08AB product, ABLIC president Mr. Tanaka made the following comments.

"We are proud to launch the new S-34HTS08AB product which supports greater data capacity in modern communications environments as the speed of the development of data communications continues to accelerate. ABLIC will continue to strive to contribute to customers around the world with highly functional and high-quality products utilizing ABLIC's unique technological capabilities."

Major Features

- 1. SPD HUB which supports I2C & I3C and is compliant with the latest JEDEC specifications

- The S-34HTS08AB supports both 3.3V/1MHz I2C communication and 1.0V/12.5MHz I3C communication. It is also an SPD HUB compliant with the latest JEDEC specifications, and can be used for a wide range of client and server DDR5 DIMMs.

In addition to the same high-reliability EEPROM and high-precision temperature sensing functions of existing DDR4, the product is also equipped with a HUB function for DDR5. This allows the product to continue to maintain temperature sensor and SPD memory roles, while also appropriately managing communications between external controllers and devices on the DIMM board to build an optimal communications system. - 2. High compatibility with peripheral devices

- The S-34HTS08AB is designed to ensure stable communications with peripheral devices, and achieves a high degree of compatibility with peripheral devices. The product has also been reviewed favorably in combinatorial testing through provision of sample products. The product can be easily combined with peripheral devices from other manufacturers in DIMM module design, greatly contributing to purchasing flexibility.

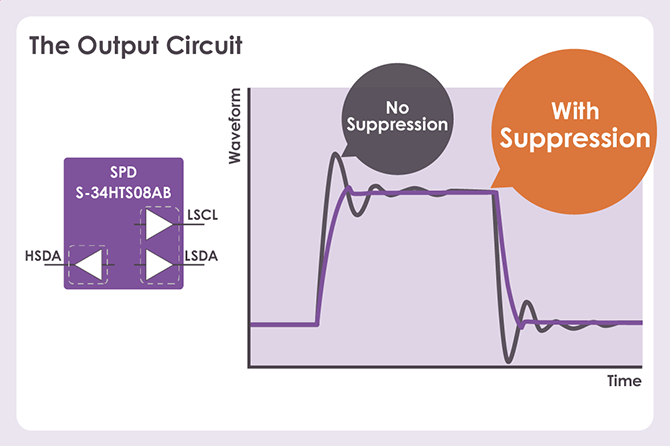

- 3. Appropriate control of input output waveforms through use of proprietary ABLIC technologies to contribute to high-speed and reliable communication

- The S-34HTS08AB is equipped with a circuit which controls communication waveforms in input circuits and output circuits. This contributes to higher speed and more reliable communication with peripheral devices.

The input circuit is designed with a dead time (time during which it does not react to oscillation) for input waveform oscillation as a countermeasure against communication noise. Communication delays are minimized through filtering.

The output circuit is equipped with an overshoot / undershoot control function which makes it possible to achieve stable output waveforms.

Major Specifications

| • Power supply voltage (VDDSPD) | : 1.70 V to 1.98 V |

|---|---|

| • Power supply voltage (VDDIO) | : 0.95 V to 1.05 V |

| • Operation frequency (I2C communication) | : 1.0 MHz max. (I/O level = 3.3 V typ.) |

| • Operation frequency (I3C communication) | : 12.5 MHz max. (I/O level = 1.0 V typ.) |

| • Operation temperature range | : Ta = -40°C to +125°C |

| • Operation temperature range (NVM write operation) | : Ta = -40°C to +95°C |

| • Memory capacity | : 8 K-bit |

| • Endurance | : 10^5 cycle / word (Ta = -40°C to +95°C) |

| • Temperature accuracy (Ta = +75°C to +95°C) | : 0.5°C typ. |

| • Temperature accuracy (Ta = +40°C to +125°C) | : 1.0°C typ. |

| • Current consumption (EEPROM in standby mode and TS in active mode) | : 0.15mA max. (VDDSPD = 1.8V) |

| • Current consumption (EEPROM in read operation mode and TS in active mode) | : 2.0mA max. (VDDSPD = 1.8V) |

| • Current consumption (EEPROM in write operation mode and TS in active mode) | : 3.0mA max. (VDDSPD = 1.8V ) |

| • Package | : DFN-8 (2030)B |

| • Hub function (*2) | |

| • Packet Error Check (PEC) function (*3) | |

| • Parity Error Check function (*4) | |

| • In Band Interrupt (IBI) function (*5) | |

| • Bus Reset function | |

| • Lead-free (Sn 100%), halogen-free | |

- (*1) JEDEC (Solid State Technology Association) is an American industrial organization which promotes the standardization of semiconductor and semiconductor product related technologies. It is most well-known for the establishment of the DDR SDRAM standard.

- (*2) A function which acts a relay for communication between external controllers and devices on the DIMM board.

- (*3) A function which allows recipients to use a dedicated 1-byte code to verify there are no errors in transmitted data.

- (*4) A function which allows recipients to use a dedicated 1-bit code to check every 1 byte of received data for errors.

- (*5) A function which allows a device with an error status to interrupt other communications to initiate its own communication.

Application Examples

- DDR5 DIMMs for data centers/servers

(RDIMM, LRDIMM, NVDIMM) - DDR5 DIMMs for clients

(SODIMM, UDIMM)

S-34HTS08AB Product details

Website

https://www.ablic.com/en/semicon/![]()

This product has been certified as a MinebeaMitsumi Group "Green Product" for its outstanding contribution to the environment.

| Contacts | ABLIC Inc. Masae Onuma E-mail: pr@ablic.com https://hub.ablic.com/en/pr-inquiry?rf=support |

|---|

Product information, contact and other context are subject to change without prior notice.